According to AMD internal slides (demonstration of performance gains within the company), AMD EPYC Milan processors built on the new Zen 3 architecture will be able to boast 20% superiority over the EPYC Rome chips based on the current Zen 2, while operating at the same frequency!

This information was shared with the public by a very reliable resource Hardwareluxx. However, this is still a rumor, so treat this data with caution.

| CPU code designation | Naples | Rome | Milan | Genoa |

| Connector | SP3 | SP3 | SP3 | SP5 |

| Number of cores/architecture | 32x Zen | 64x Zen 2 | 64x Zen 3 | >64x Zen 4 |

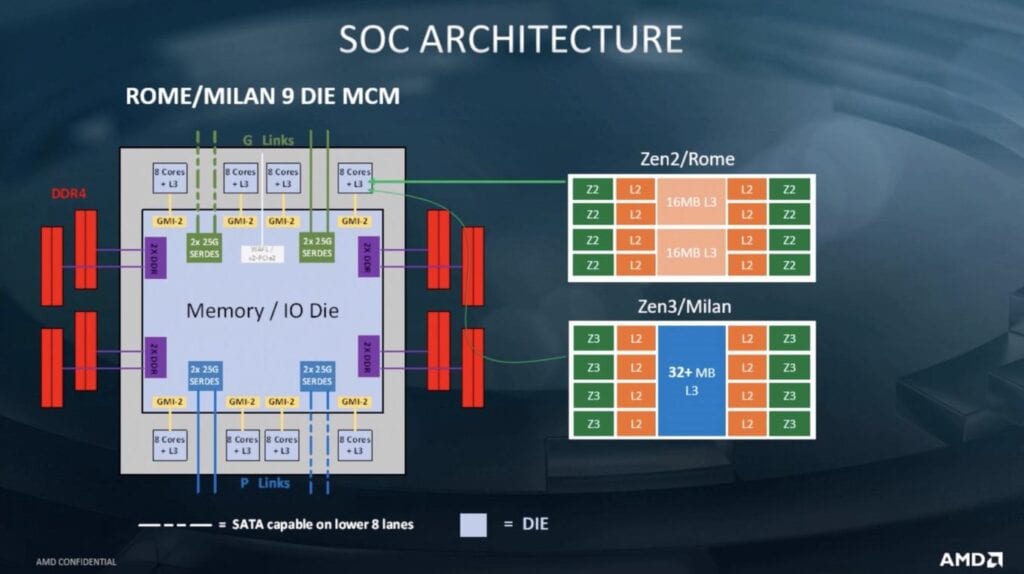

| CCD / L3-Кэш | 8 ядер на CCD 2x 16 MB L3-Cache | 8 ядер на CCD 2x 16 MB L3-Cache | 8 ядер на CCD 1x 32 MB L3-Cache | – |

| Technical process | 14 nm | 7 nm | 7 nm | 5 nm |

| RAM support | DDR4 | DDR4 | DDR4 | DDR5 |

| PCI-e version | PCIe 3.0 | PCIe 4.0 | PCIe 4.0 | PCIe 5.0 |

| TDP | 120 – 180 W | 120 – 225 W | 120 – 225 W | 120 – 240 W |

According to the report, AMD’s Zen 3 architecture will allow for 15% IPC gains. However, it should be understood AMD takes a different approach to EPYC Milan processors. For example, 64-core solutions can get a 15% increase in performance, but 32-core solutions have a more impressive 20% increase compared to their current counterparts.

In addition, if earlier in each of the two CCXs there was its own third-level cache of 16MB, now it will become common, and its volume will be 32MB (in fact, the size of the cache on the CCD will not change, but it will become faster). This change should significantly affect the overall performance of the CPU since the cores will not have to access the necessary information in the cache memory of another CCX.